Fraunhofer Institute for Reliability and Microintegration IZM

Forschungsfabrik Mikroelektronik Deutschland

# The APECS pilot line is powering the evolution of chiplet technologies

Fraunhofer Group for Microelectronics in cooperation with the Leibniz Institutes FBH and IHP

Rolf Aschenbrenner Fraunhofer IZM Deputy Director Rolf.aschenbrenner@izm.fraunhofer.de **European Chips Act and the FMD Pilot Line: APECS**

Pilot Line for Advanced Packaging and Heterogeneous Integration for Electronic Components and Systems (APECS)

# EU Chips Act, Nov. 30th 2023 Implementation via 3 Pillars

# The EU chips act aims to:\*

- → ensure large-scale capacity building and innovation within the EU

- → ensure that the EU is self-supplying to a much greater extent

- → ensure that the EU can react quickly in the event of supply crises

\*Source: European Commission, Eurpean Parliament, Statista European Union, 2022

ouncil of the European Union

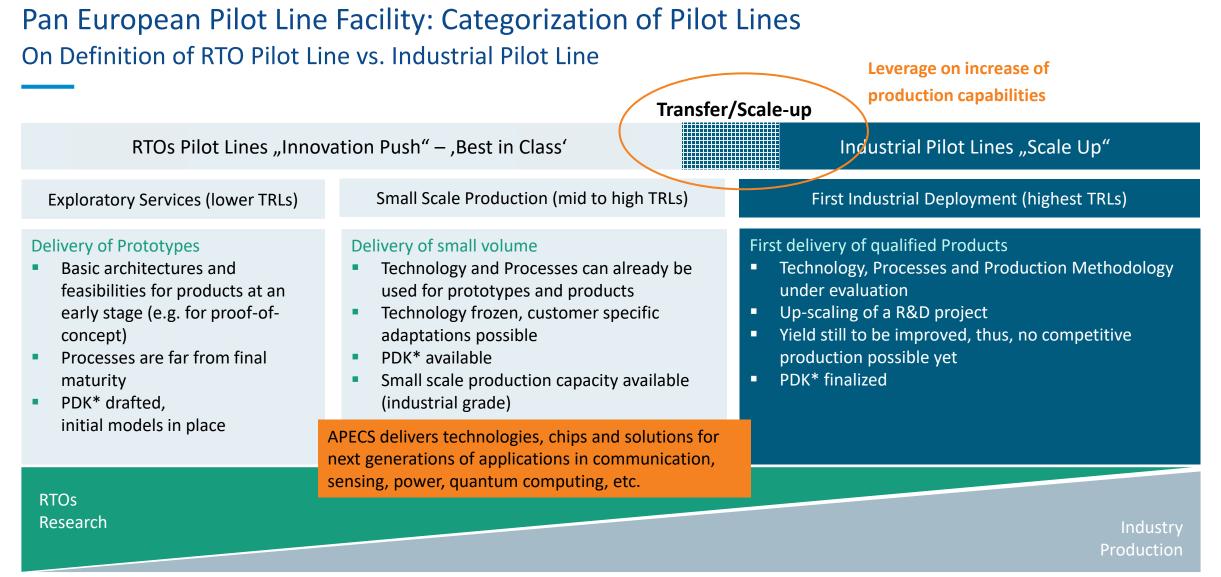

\* PDK: process design kit, model of the fabrication process to be used for the chip design

# The APECS pilot line – European chiplet innovation

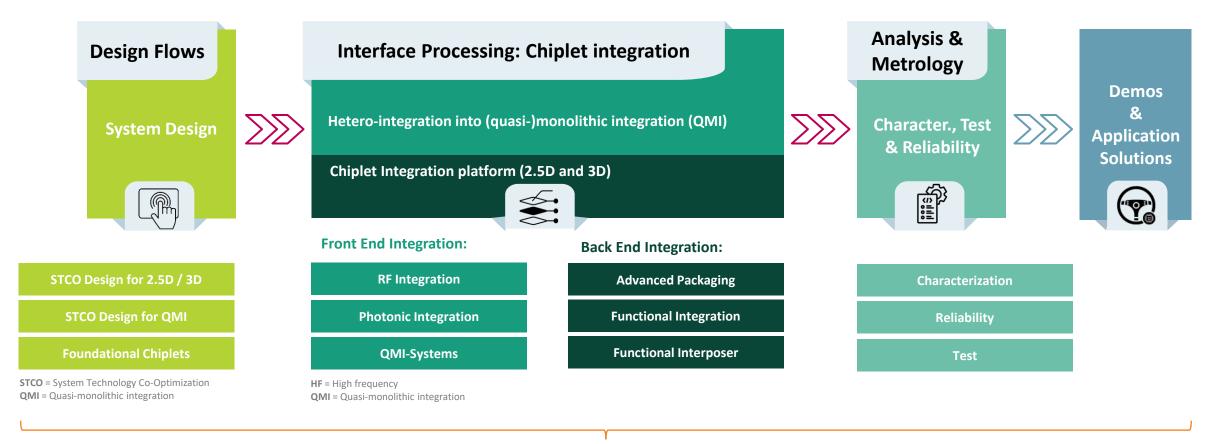

How APECS leads the way in heterogeneous integration by providing diverse design capabilities, technologies and testing strategies for electronic components and systems on a single platform

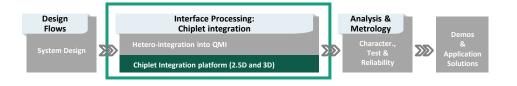

# FMD Pilot Line APECS Working Packages

## **One-Stop-Shop**

# Fraunhofer IZM – Merging of Wafer- and Panel-Level Technologies

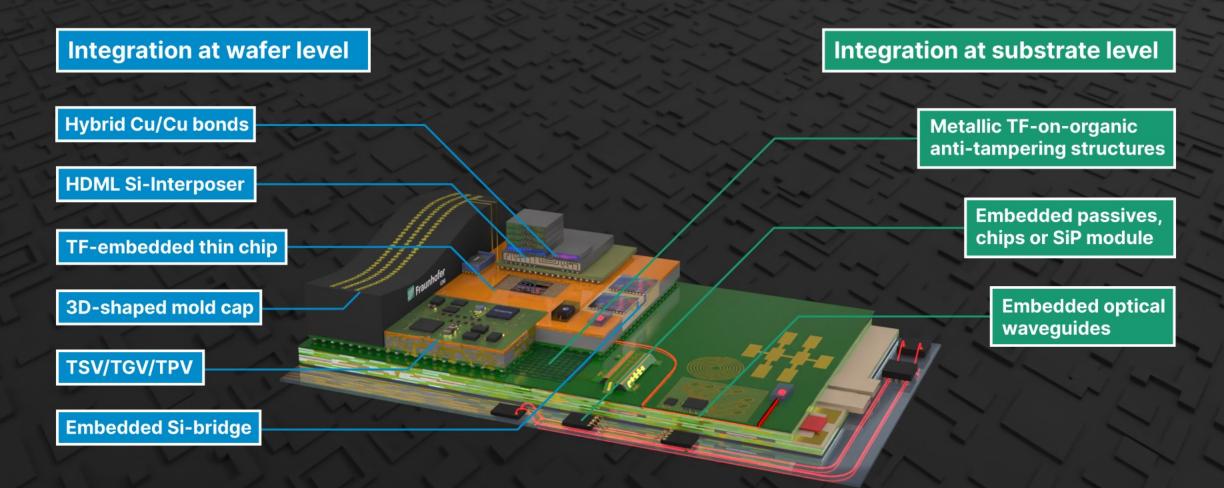

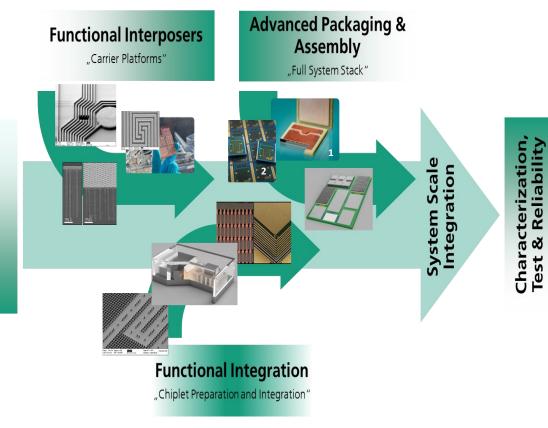

## Fraunhofer – Heterogeneous Integration From Wafer Level System Integration to Panel Level System Integration

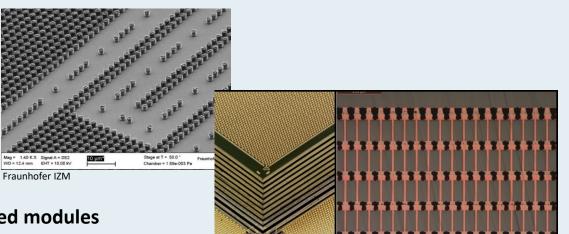

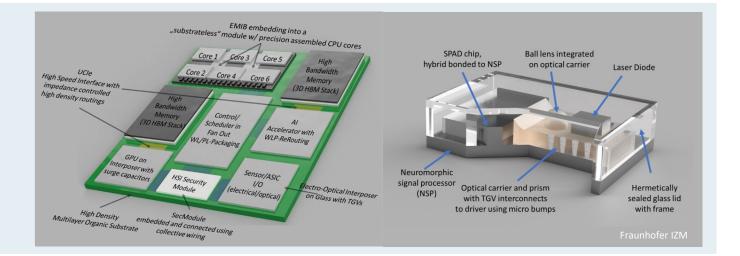

Illustration of possibilities and the complexity of advanced heterogeneous system integration and advanced packaging

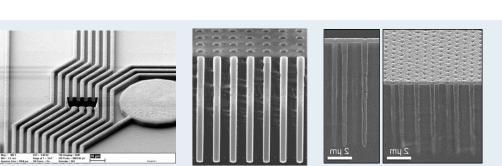

## **Examples for the integration at wafer and substrate level**

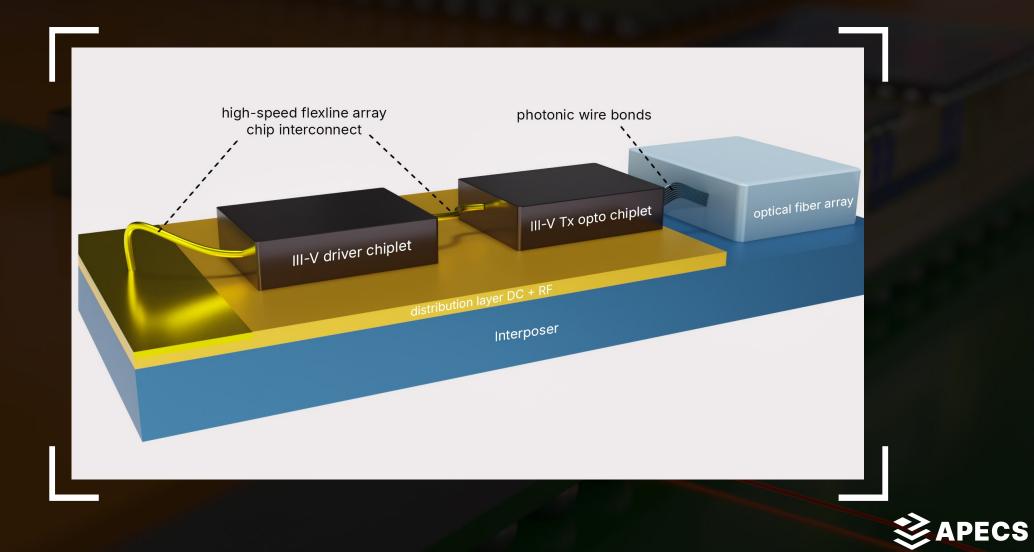

Integration of opto-electronic components as an example of photonic systems

# **Opto Demonstrator**

11

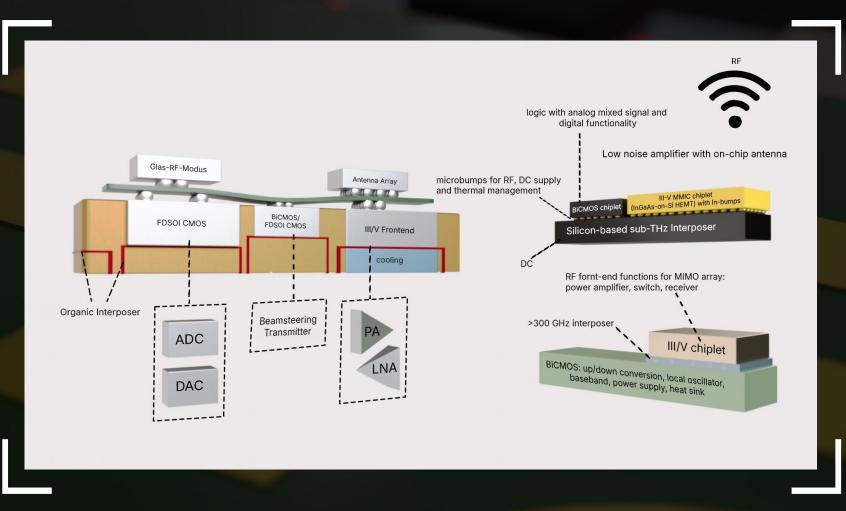

# Integration of RF antennas as an example for RF systems

# **3 RF subdemonstrators for different wavelengths**

## **3 RF subdemonstrators for different wavelengths**

## Target

D-band transceiver with bipolar InP chiplet on a SiGe-BiCMOS chip for 6G

- H-band transceiver with an InGaAs-on-Si-HEMT chiplet and BiCMOS chiplet on a Si-based sub-THz carrier substrate

- D-band radar transceiver module using a BiCMOS radar chiplet and an RF glass interposer with deposited antenna structure

## Innovations

- InP chiplets on SiGe-BiCMOS

- Fan-Out WLP embedding, which allows the integration of different semiconductor technologies

- RF-flex interposer technology

## Impact

## 6G wireless communication:

- D-band transceiver

- H-band transceiver

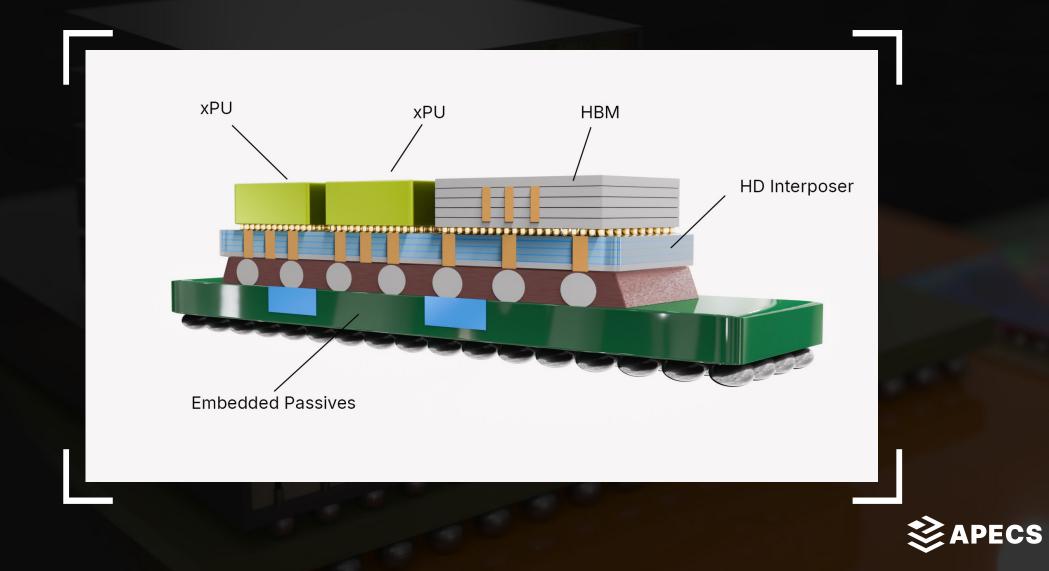

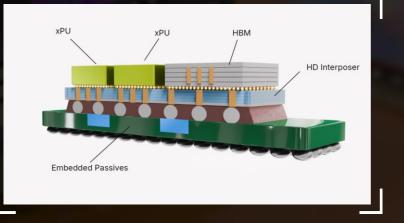

Integration of a 3D-Si-Stack as an example for highperformance computing

# **HPC Demonstrator**

## **HPC Demonstrator**

## Target

- STCO concept for HPC

- Silicon interposer(s) equipped with e.g. several compute- and accelerating-units and high bandwidth memory (HBM)

## Impact

- HPC concepts for multiple applications

- Reduced development time by STCO

## Innovations

- High speed, low-power and short distance die-to-die (D2D) data lanes between chiplets and memory stacks on Si/Glass and organics substrates

- Optimized signal and power integrity

Key innovations of the APECS pilot line

## Key innovations of the APECS pilot line

1

Worldwide first **advanced automotive chiplet integration platform** (2.5D and 3D) for multiple core technologies (CMOS, Opto/RF) and non-electronic devices (MEMS, Opto, OLED), leveraging the innovations of advanced packaging

2

**Comprehensive end-to-end design flow and methodology** for chiplet-based advanced heterogeneous systems integration – Design-for-Performance, -Yield, -Power Efficiency, -Testability

3

Expansion of hetero-integration into **quasi-monolithic integration (QMI) for highest performance density** by leveraging Back-End-of-Line and Advanced Packaging capabilities 4

Prototyping of **high performance chiplet-based systems for specific needs of the European industries**, in particular, automotive, medical device and health care, sensors and advanced manufacturing industries

Novel backend-of-line interfacing technology for MEMS, opto/RF chips (III/V RF chiplets with (Bi)CMOS for 100 GHz+ frequencies)

**Novel testing concepts and technologies** for function-, quality- and yield- optimization

# Workpackage: Chiplet Fabrication

**Characterization Test Reliability**

Chiplet Interface Readiness for Heterogeneous Integration

Chiplets from external partners (RTOs, IDMs, Foundries,...)

> Compute and Memory Integration Photonics Integration

**RF** Integration

QMI System Int<u>egration</u>

**MEMS** Integration

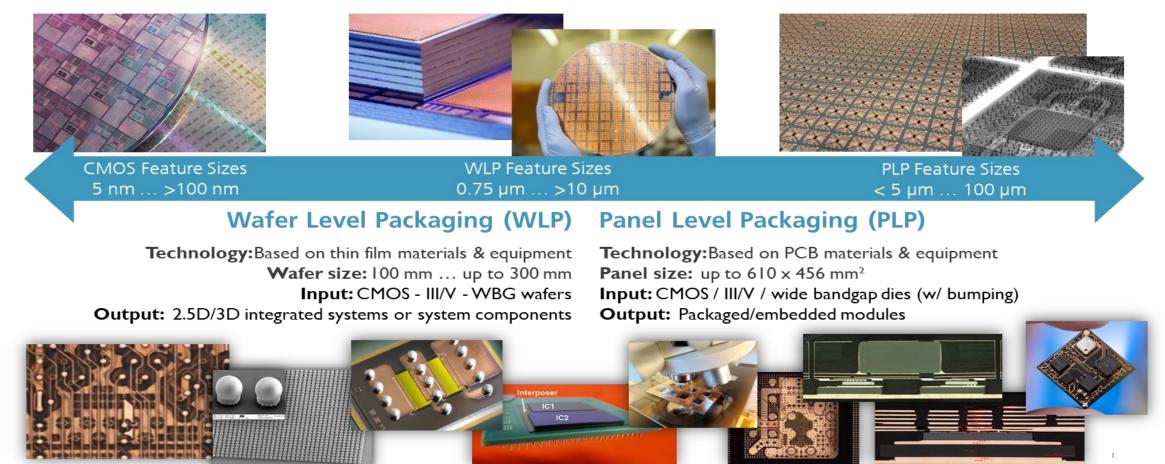

## Wafer Level Packaging (WLP)

Based on thin film materials & equipment 100mm ... up to 300 mm CMOS – III / V - WBG wafers 2.5D / 3D integrated systems

Volker Mai / Fraunhofer IZM

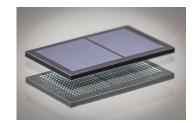

## Panel Level Packaging (PLP)

Based on PCB materials & equipment up to 610 x 456 mm<sup>2</sup> CMOS - III / V - WBG dies (w/ bumping) Packaged / embedded modules

**APECS Demonstrators**

Fraunhofer IZM

Demonstrators

**Characterization Test Reliability**

Fraunhofer IZM

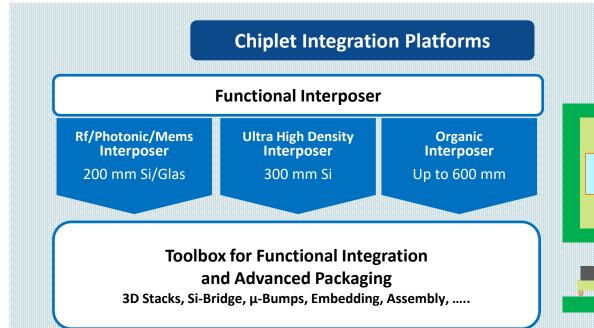

# Chiplet Integration Platform Functional Interposer

## Target

- Anorganic Interposers for advanced CMOS on 300mm

- Multi-Functional Interposers for RF, Optoelectronics & MEMS\*

- Passive Functionalities in Interposer

- Organic HD Interposers

- Providing all required technologies for interposers based chiplet integration

#### Innovations

- Sub-micron TSV's, AR20:1,UHD Routing incl. PostCMOS

- Glass, HR-Si, Ceramics with TxV's and resp. routing, on 200mm

- IPDs, integrated cooling, LWGs, structural features

- Advanced HD substrates (5μm L/S)

- Laminates with embedded IC

- Panel Scale Interposers using FO processes

#### Impact

Design

Flows

- Preparation for UHD Wafer Scale Integration, supporting QMI and Advanced Packaging

- Interposers serving Multi-Domain Systems (MEMS, Opto, RF, Sensing, \*) for broad range of functionalities

- Critical functionalities integrated in a single process flow

- Module- and System Interfaces towards the applications

\* Power Electronics is served but was excluded from the text due to potential interference with the PowerSemiconductor Pilot Line

All pictures: Fraunhofer IZM

# Chiplet Integration Platform Functional Integration

- 3D Stacking of advanced CMOS wafers and non-CMOS heterogenous/multimaterial wafers

- 2.5D Integration of chiplets onto interposer

- Preparation for chiplet interfaces

- Specific technologies for MEMS and sensor chiplets

- Providing all technologies to realize heterogeneously integrated modules

Interface Processing:

Chiplet integration

Chiplet Integration platform (2.5D and 3D

-integration into ON

Fraunhofer IZM

#### Innovations

- High density Wafer2Wafer stacking with sub µm precision using hybrid bonding

- Stack-integration of specific functionalities for HIS providing hermeticity, capping

- Die2Wafer integration for heterogenous functionalities

- Chiplet interface adaption with RDLs, terminal metal & bumps

## Impact

Design

Flows

- Chiplet based module realization with functionalities from different domains

- Highest density integration of heterogenous chiplets

- Enabling STCO methodology throughout domains

Analysis &

Metrology

# Chiplet Integration Platform Advanced Packaging & Assembly

#### Target

- System scale assembly for Heterosystems with Modules and Subsystems

- Quality and Reliability assured functionalities at system level

- Novel integration concepts for 3D volumetric systems

#### Innovations

- High density, high speed, assembly on advanced substrates

- Reliable assembly for multi-layered heterogenous systems

- Embedded and fan out integration of systems

- Hybrid integration concept using embedding and fan out on panel scale

- Layer-by-Layer stacking for 3D volumetric system integration

#### Impact

Fraunhofer IZM

- Functional highly integrated for novel applications autonomous mobility, RF and Communication, Sensors, Power and Photonics

- Supporting STCO methodology

# WP Chiplet Integration: Service Offer

Copyrights: 1,2: Volker Mai, Fraunhofer IZM, all others: Fraunhofer IZM

- 2.5 and 3D stack HD integration of heterogeneous devices for silicon and non-silicon devices with μTSVs in the sub-μm range using microbumps and hybrid bonding innovations

- MEMS and Sensor Integration with 3D stacked chiplets up to 300 mm wafers for highly functional modules

- Scale-up of process implementation using embedding technologies into advanced substrates up to 600mm

- Module and subsystem integration HPC, NGC, Power-E, Sensors, UWBG & RF/Opto from chiplet to substrate

- Scale-up of process implementation for high-end chiplet architectures

(3D, 2.5D) up to 600 mm

- **Open Access** for other Pilot Lines, RTO's and industry to facilitate early adoption of new technologies & fast-track innovations

Chiplets

## **Executive Summary**

**FMD Pilot Line APECS**

Strong benefits for European industry and RTOs

# Thanks for Your Attention Contact

Rolf Aschenbrenner Fraunhofer IZM Deputy Director Rolf.aschenbrenner@izm.fraunhofer.de

Fraunhofer Institute for Reliability and Microintegration IZM

## **APECS Business Office**

**c/o Research Fab Microelectronics Germany** Anna-Louisa-Karsch-Str. 2 10178 Berlin (Germany)

27

Please feel free to discuss your request with our experts: experts@apecs.eu

apecs.eu